Pub手册4.2.4,DDR接口中的阻抗校准过程,涉及如何通过控制逻辑、专用的单元和总线来实现对SSTL(Stub Series Terminated Logic)信号的阻抗调节。这个过程确保信号在传输过程中能维持正确的阻抗,以优化信号的质量和稳定性。

阻抗控制器模块

提供了必需的阻抗控制功能,能够使功能性SSTL单元的可编程和PVT补偿的ODT(On-Die Termination,片内终端)以及输出阻抗得到有效控制。具体包括以下几种控制选项:

1. Sample-based tracking of RZQ:

- RZQ 是指阻抗参考电阻值,通常与DDR总线的阻抗匹配有关。该功能表示通过采样来跟踪RZQ的变化,以保证SSTL接口的稳定信号传输,并使阻抗回路电路能够在较低功耗下稳定运行。

2. Impedance code override:

- 该功能允许直接控制阻抗代码(Impedance Code)。这些阻抗代码是用来控制SSTL信号的驱动阻抗的,这项功能使得用户能够绕过自动控制,手动设置阻抗,从而有更多的灵活性和控制。

3. Impedance code output:

- 通过输出阻抗代码,用户可以监控控制回路的操作情况。这意味着可以实时查看当前控制回路在调节阻抗时的状态,帮助调试和优化。

4. Programmable divide on the input clock signal:

- 这项功能提供了一个可编程的分频器,可以在输入时钟信号上进行分频。通过分频,可以实现稳定的操作,适应不同频率范围的输入时钟。这对于支持高频信号的稳定性非常重要。

5. Automatic sequencing for independent impedance compensation:

- 该功能会自动进行独立的阻抗补偿,针对四个不同的阻抗元素进行逐一补偿:

- ODT(On-Die Termination)拉高/拉低电阻

- 输出阻抗拉高/拉低

- 这样可以确保每个阻抗元素在不同操作状态下都能得到最佳的匹配与补偿。

6. Programmable asymmetric drive strength and pullup-only termination calibration:

- 支持可编程的不对称驱动强度调节和仅拉高终止校准。也就是说,用户可以对SSTL接口的驱动强度进行调节,以应对不同的负载需求。

7. VT drift detection and automatic DFI update request:

- VT drift(电压漂移)指的是随着温度、工艺变化,电压参考点可能发生的漂移。这项功能能够检测到电压漂移,并在发现漂移时,自动发出DFI(DDR接口)更新请求,以调整内存接口的配置,确保系统始终稳定运行。

8. Code averaging support for smoother code transitions:

- 支持代码平均(Code Averaging),用来平滑阻抗代码的过渡。这意味着当阻抗代码变化时,变化的过程会更为平滑,从而避免因突变引起的信号不稳定。

9. Programmable drive strength adjustment for pullup drive and pulldown drive strengths:

- 允许用户调节驱动强度,分别调整拉高和拉低的驱动强度。这使得在不同的工作条件下,SSTL接口能够适应各种负载,从而优化信号的完整性和稳定性。

关键组件和流程

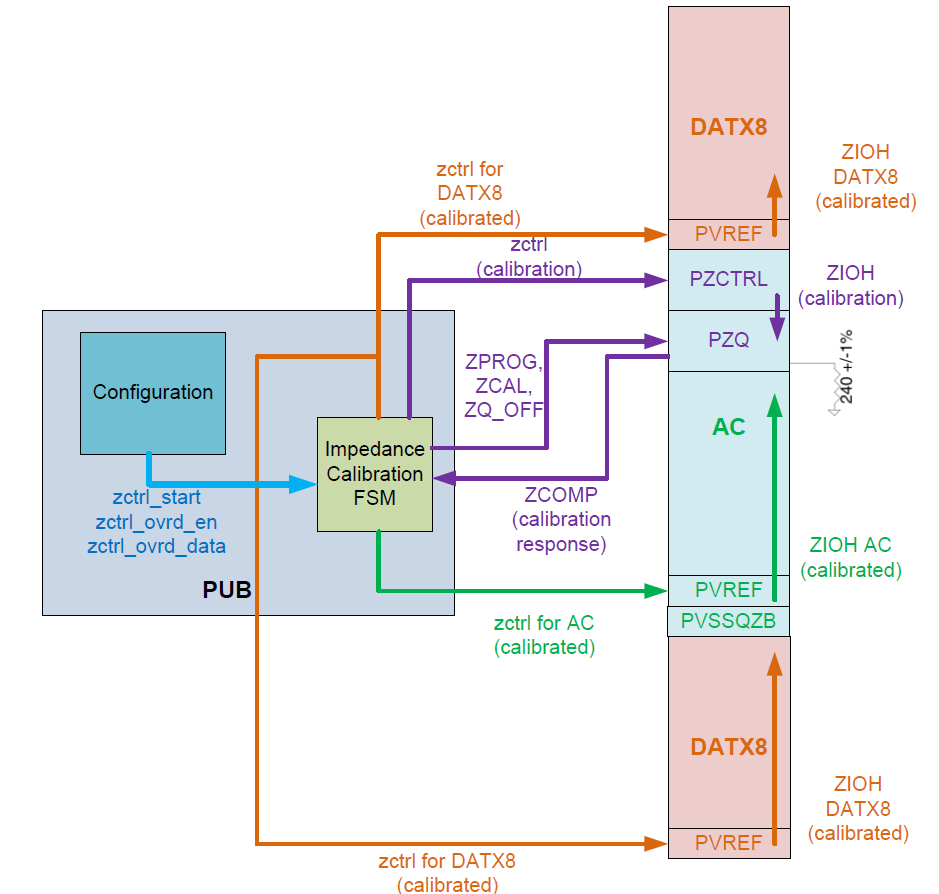

1. PZQ单元与PZCTRL单元的配合

- 一个PZQ(Programmable Impedance)单元和一个PZCTRL单元可以用于一个或多个SSTL组,这些SSTL组需要独立的驱动阻抗和ODT(On-Die Termination,芯片内终端电阻)阻抗控制。

- 每个PZCTRL单元必须与一个PZQ单元配对使用,这两个单元的协作用于控制信号的阻抗。

2. PVSSQZB单元和ZIOH总线

- PVSSQZB单元用来创建一个独立的ZIOH总线段,专门用于阻抗校准。ZIOH总线是连接各个阻抗控制单元的总线,确保信号的正确传输。

- 在没有连接阻抗控制逻辑的接口段中,PVREF单元不能使用。这是为了避免信号干扰和不必要的电压参考误差。

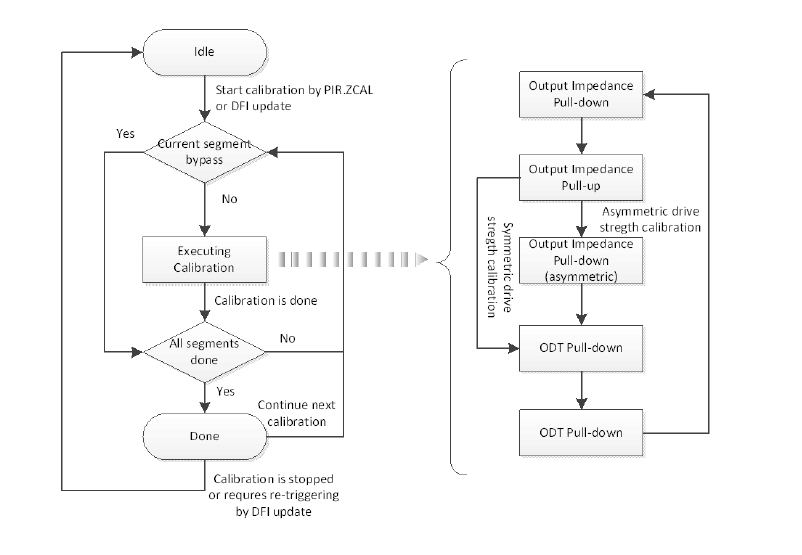

3. 阻抗校准触发与绕过

- 通过PIR寄存器的ZCALBYP位,可以随时绕过阻抗校准过程。

- 如果校准被绕过,那么阻抗需要在稍后的时间通过重新触发校准或直接编程控制寄存器ZQnDR来进行重新校准。

4. 阻抗校准流程

一旦触发校准,阻抗校准逻辑会按照以下顺序依次校准四个阻抗元素:

- 输出阻抗拉低(pull-down)

- 输出阻抗拉高(pull-up)

- ODT拉低(pull-down)

- ODT拉高(pull-up)

对每个阻抗元素,阻抗控制逻辑会通过ZCTRL总线发送一个阻抗代码到PZCTRL单元,然后PZCTRL单元将这些数据进行编码并转换电平,传送到SSTL单元中的功能性I/O单元和PZQ单元。

5. PZQ单元与外部电阻的匹配

- PZQ单元接收到来自PZCTRL单元的控制代码,并与外部电阻进行比较,从而确定最佳的阻抗值。

- PZQ单元还接收到PUB(PHY控制器)的分频比(ZPROG),用于调整阻抗校准的精度。

- 当PZQ单元计算出阻抗匹配情况后,会将zcomp值反馈给阻抗控制逻辑,阻抗控制逻辑会根据反馈值更新控制代码,继续优化阻抗。

6. 闭环控制

- 阻抗控制过程是一个闭环控制系统。每次校准都会根据反馈信息调整阻抗代码,直到找到最匹配的阻抗值为止。

- 一旦一个阻抗元素的校准完成,逻辑会自动开始下一个阻抗元素的校准。

7. 错误监控和完成状态

- 在校准过程中,用户可以通过ZQnSR寄存器监控回路状态,检查是否有错误。

- 当所有四个阻抗元素的校准完成后,逻辑会在**PGSR[ZCDONE]**寄存器的**ZCDONE**位中标记“完成”状态,表示校准成功。

8. 时钟控制

- 校准逻辑使用PUB控制器时钟作为采样时钟来控制阻抗校准回路的操作。由于这个回路不需要高频操作,因此通常使用较低的时钟频率来保证稳定性。

- 该回路的频率比PUB时钟低得多,阻抗控制模块包含一个可编程时钟计数器,用于控制等待一定的时钟周期再进行采样。

9. 背景运行与DFI更新

- 校准初始化完成后,阻抗校准会继续在后台运行,周期性地进行DFI控制和PHY更新,将更新后的VT(Voltage Threshold,电压阈值)代码传播到DDR接口上的I/O单元。

总结:

这段描述的内容主要讲述了DDR接口阻抗校准的流程,以及如何通过一系列专用单元和总线实现对信号阻抗的精确调节。通过这个校准过程,信号的阻抗可以被精确地控制和优化,从而确保DDR接口能够稳定高效地工作。这个过程不仅考虑了不同工艺、电压和温度的变化,还确保了校准的反馈是闭环的,能够实时调整,最终达到最佳的阻抗匹配效果。

本文链接: https://talent-tudou.github.io/2024/11/09/DDR/PUB Architecture-Impedance Calibration/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!